- 您现在的位置:买卖IC网 > Sheet目录1917 > DSPIC30F3013-20I/ML (Microchip Technology)IC DSPIC MCU/DSP 24K 44QFN

PIC18F46J11 FAMILY

DS39932D-page 158

2011 Microchip Technology Inc.

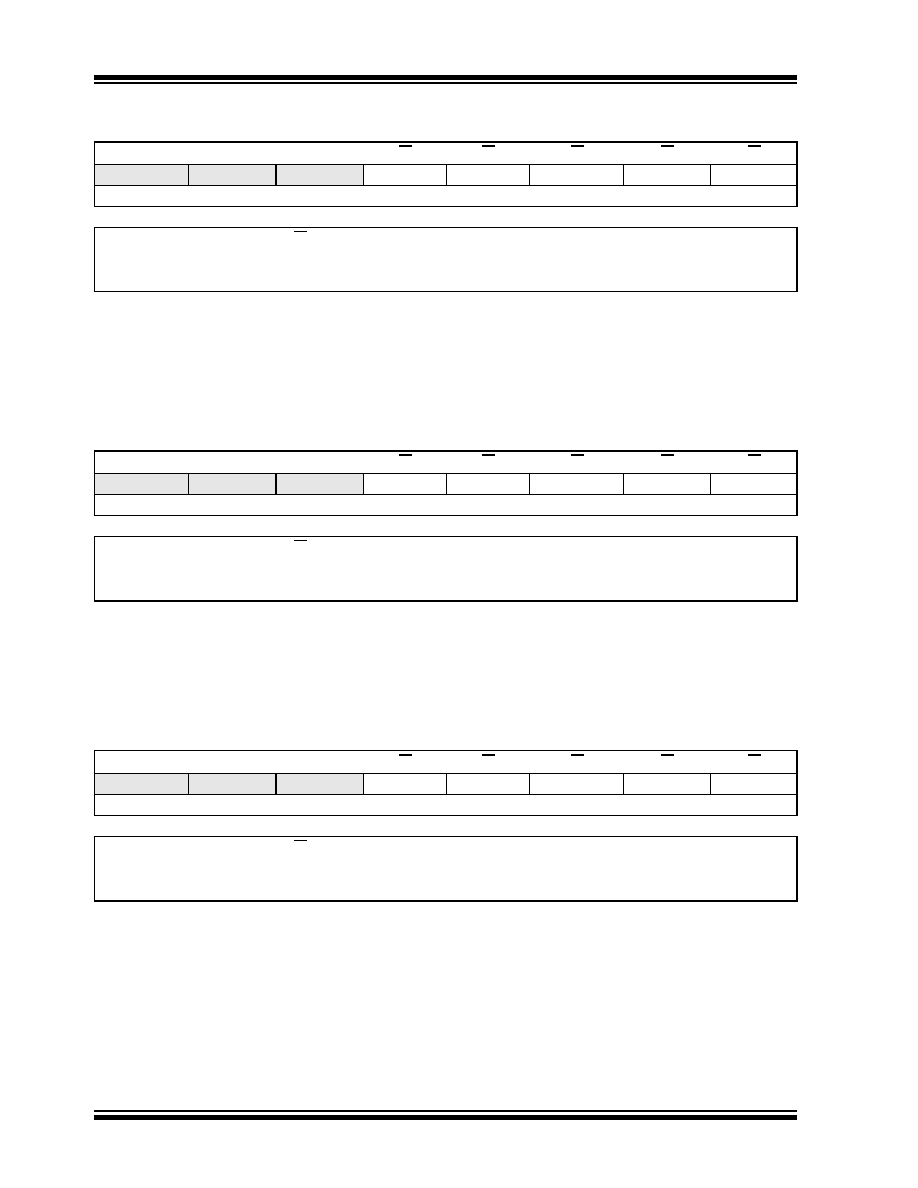

REGISTER 10-12: RPINR8: PERIPHERAL PIN SELECT INPUT REGISTER 8 (BANKED EEEh)

U-0

R/W-1

—

IC2R4

IC2R3

IC2R2

IC2R1

IC2R0

bit 7

bit 0

Legend:

R/W = Readable, Writable if IOLOCK = 0

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as ‘0’

-n = Value at POR

‘1’ = Bit is set

‘0’ = Bit is cleared

x = Bit is unknown

bit 7-5

Unimplemented:

Read as ‘0’

bit 4-0

IC2R<4:0>:

Assign Input Capture 2 (ECCP2) to the Corresponding RPn Pin bits

REGISTER 10-13: RPINR12: PERIPHERAL PIN SELECT INPUT REGISTER 12 (BANKED EF2h)

U-0

R/W-1

—

T1GR4

T1GR3

T1GR2

T1GR1

T1GR0

bit 7

bit 0

Legend:

R/W = Readable, Writable if IOLOCK = 0

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as ‘0’

-n = Value at POR

‘1’ = Bit is set

‘0’ = Bit is cleared

x = Bit is unknown

bit 7-5

Unimplemented:

Read as ‘0’

bit 4-0

T1GR<4:0>:

Timer1 Gate Input (T1G) to the Corresponding RPn Pin bits

REGISTER 10-14: RPINR13: PERIPHERAL PIN SELECT INPUT REGISTER 13 (BANKED EF3h)

U-0

R/W-1

—

T3GR4

T3GR3

T3GR2

T3GR1

T3GR0

bit 7

bit 0

Legend:

R/W = Readable, Writable if IOLOCK = 0

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as ‘0’

-n = Value at POR

‘1’ = Bit is set

‘0’ = Bit is cleared

x = Bit is unknown

bit 7-5

Unimplemented:

Read as ‘0’

bit 4-0

T3GR<4:0>:

Timer3 Gate Input (T3G) to the Corresponding RPn Pin bits

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

DSPIC30F4011-30I/ML

IC DSPIC MCU/DSP 48K 44QFN

DSPIC30F4013-30I/ML

IC DSPIC MCU/DSP 48K 44QFN

DSPIC30F5013-30I/PT

IC DSPIC MCU/DSP 66K 80TQFP

DSPIC30F5015-30I/PT

IC DSPIC MCU/DSP 66K 64TQFP

DSPIC30F6010-20E/PF

IC DSPIC MCU/DSP 144K 80TQFP

DSPIC30F6010A-30I/PF

IC DSPIC MCU/DSP 144K 80TQFP

DSPIC30F6013A-30I/PF

IC DSPIC MCU/DSP 132K 80TQFP

DSPIC30F6014-30I/PF

IC DSPIC MCU/DSP 144K 80TQFP

相关代理商/技术参数

dsPIC30F3013-20I/SO

功能描述:数字信号处理器和控制器 - DSP, DSC 28LD 20MIPS 24 KB RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

dsPIC30F3013-20I/SP

功能描述:数字信号处理器和控制器 - DSP, DSC 28LD 20MIPS 24 KB RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

DSPIC30F3013-30I/ML

功能描述:数字信号处理器和控制器 - DSP, DSC Sensor RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

DSPIC30F3013-30I/SO

功能描述:数字信号处理器和控制器 - DSP, DSC Sensor RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

DSPIC30F3013-30I/SO

制造商:Microchip Technology Inc 功能描述:IC DSC 16BIT 24KB 40MHZ 5.5V SOIC-28

DSPIC30F3013-30I/SP

功能描述:数字信号处理器和控制器 - DSP, DSC Sensor RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

DSPIC30F3013-30I/SP

制造商:Microchip Technology Inc 功能描述:16-Bit Digital Signal Controller

dsPIC30F3013T-20E/ML

功能描述:数字信号处理器和控制器 - DSP, DSC 44LD 20MIPS 24 KB RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT